Technical Specifications

Parameters and characteristics commom to parts in this series

| Specification | TMS320C44GFW60 | TMS320 Series |

|---|---|---|

| - | - | |

| Clock Rate | 60 MHz | 1 - 1000 MHz |

| Clock Rate | - | 1 - 600 GHz |

| Clock Rate | - | 1.2 GHz |

| Clock Rate | - | 720 MHz |

| Connectivity | - | uPP, SPI, UART/USART, I2C, McBSP, CANbus, USB, SCI, EBI/EMI |

| Connectivity | - | CANbus |

| Connectivity | - | UART/USART |

| Connectivity | - | SCI |

| Connectivity | - | SPI |

| Connectivity | - | I2C |

| Connectivity | - | McBSP |

| Connectivity | - | UART/USART, SCI, SPI, CANbus, I2C, LINbus, EBI/EMI, USB, McBSP, uPP |

| Connectivity | - | USB |

| Core Processor | - | C28x, C2xx DSP |

| Core Size | - | 32-Bit Single-Core, 16-Bit |

| Core Size | - | 32-Bit Dual-Core |

| Data Converters | - | D/A 3x12b |

| Data Converters | - | A/D 14x12b |

| Data Converters | - | 10 - 12 bits |

| Data Converters | - | 1 - 24 |

| Data Converters | - | 12 - 16 b |

| Data Converters | - | 12 b |

| Data Converters | - | A/D 16x10b, A/D 20x16b, D/A 3x12b, A/D 20x12b, A/D 8x12b, A/D 24x12b, 12x16b, A/D 17x12b, A/D 14x16b, A/D 14x12b |

| Data Converters | - | 10 b |

| Data Converters | - | 20x12b, 9x16b |

| Data Converters | - | 3x12b |

| Data Converters | - | 5 |

| Grade | - | Automotive |

| Interface | Communication Ports | ASP, UART, SPI, USB, I2C, Ethernet MAC, Host Interface, UTPOIA, Telecom, McBSP, SSP, BSP, MMC/SD, I2S, EBI/EMI, UART/USART, Communication Ports, Parallel, TDM, HPI, Host Interface, McBSP, UTOPIA, PCI, McASP, 10/100 Ethernet MAC, SCI, CAN, 10/100/1000 Ethernet MAC, Ethernet, PCIe, 10/100/1000 Ethernet, TSIP, SRIO, Serial Port, LCD, Serial ATA, SD/SDIO, SATA, MMC/SD/SDIO, UPP, DDR3, Duplex Serial Port, McSPI, UHPI |

| Mounting Type | Surface Mount | Surface Mount, Through Hole |

| Non-Volatile Memory | External | ROM, External, FLASH |

| Non-Volatile Memory | - | 8 kB |

| Non-Volatile Memory | - | 1.088 - 768 kB |

| Number of I/O | - | 13 - 169 |

| On-Chip RAM | 8 kB | 1 - 896 kB |

| Operating Temperature [Max] | 85 °C | 70 - 125 °C |

| Operating Temperature [Min] | 0 °C | -55 - 0 °C |

| Oscillator Type | - | Internal, External |

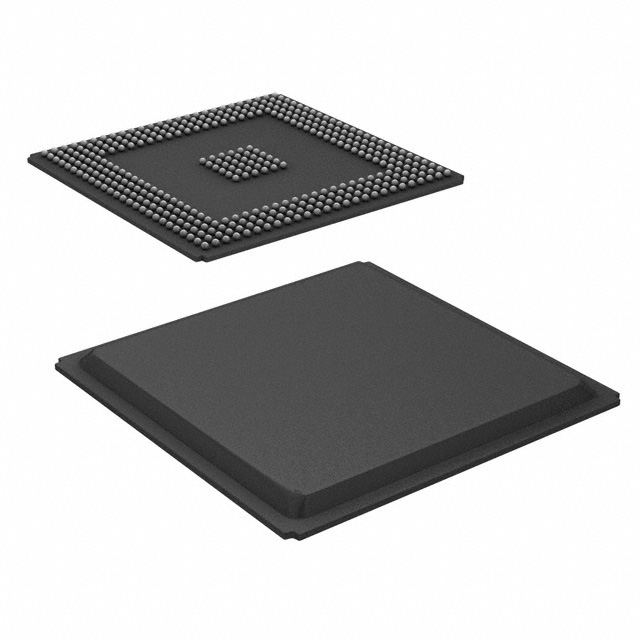

| Package / Case | 388-BBGA | 337-LFBGA, 100-TQFP Exposed Pad, FCBGA, 737-BFBGA, FCBGA Exposed Pad, 352-BBGA, 100-LQFP, 196-LFBGA, 304-BFQFP Exposed Pad, 305-BFCPGA Exposed Pad, 128-LQFP, 80-LQFP, 144-LQFP, 176-LQFP, 532-BFBGA, 361-LFBGA, 697-BFBGA, 684-BFBGA, 376-BBGA Exposed Pad, 529-BFBGA, 56-VFQFN Exposed Pad, 48-LQFP, 176-LFBGA, 841-BFBGA, 548-BFBGA, 132-BQFP Bumpered, 144-LFBGA, 272-BBGA, 561-BFBGA, FCCSPBGA, 176-LQFP Exposed Pad, 338-LFBGA, 144-BQFP, 176-BGA, 384-BFBGA, 64-TQFP, 352-LBGA, 1031-BFBGA, 256-BGA, 100-BQFP, 257-LFBGA, 240-LFBGA, 325-BFCPGA Exposed Pad, 625-BFBGA, 288-BBGA, 80-TQFP Exposed Pad, 548-BBGA, 38-TSSOP (0.240", 6.10mm Width), 388-BBGA, 144-TQFP Exposed Pad, 100-LFBGA, 64-BQFP, 68-LCC (J-Lead), 288-LFBGA, 201-LFBGA, 169-LFBGA, 384-FBGA, 32-LQFP, 181-BCPGA Exposed Pad, 688-BFBGA, 80-BQFP, 40-DIP, 208-LQFP Exposed Pad, 44-LCC (J-Lead), 68-BCPGA Exposed Pad, 181-CPGA, 143-VFBGA, 340-FBGA Exposed Pad |

| Package / Case | - | 0.6 - 600 in |

| Peripherals | - | WDT, DMA, POR, PWM, Brown-out Detect/Reset |

| Program Memory Size | - | 1 - 512 KB |

| Program Memory Type | - | FLASH, ROMless |

| Qualification | - | AEC-Q100 |

| RAM Size | - | 2 - 102 K |

| RAM Size | - | 10K x 16, 1K x 8, 82K x 16, 4K x 16, 5K x 8 |

| Speed | - | 20 - 200 MHz |

| Supplier Device Package | 388-BGA (35x35) | 337-BGA (13x13), 100-HTQFP (14x14), 352-FCBGA (27x27), 100-LQFP (14x14), 196-NFBGA (10x10), 304-PQFP, 305-CPGA (47.25x47.25), 128-LQFP (14x14), 144-LQFP (20x20), 176-LQFP (24x24), 532-FC/CSP (23x23), 361-NFBGA (16x16), 179-NFBGA (12x12), 697-FCBGA (24x24), 684-FCBGA, 376-BGA (23x23), 529-FCBGA (19x19), 56-VQFN (7x7), 48-LQFP (7x7), 176-BGA MICROSTAR (15x15), 841-FCBGA (24x24), 548-FC/CSP (23x23), 132-BQFP, 361-NFBGA (13x13), 144-BGA MICROSTAR (12x12), 272-BGA, 561-FC/CSP (23x23), 176-HLQFP (24x24), 338-BGA (13x13), 179-BGA MICROSTAR (12x12), 144-QFP (28x28), 176-BGA (15x15), 384-FCBGA (18x18), 64-TQFP (10x10), 352-BGA (35x35), 1031-FCBGA (25x25), 532-FCBGA (23x23), 256-BGA, 256-BGA (17x17), 100-QFP (20x14), 337-NFBGA (16x16), 257-BGA MICROSTAR (16x16), 561-FCBGA (23x23), 240-BGA MICROSTAR (15x15), 325-CPGA (47.25x47.25), 144-NFBGA (12x12), 625-FCBGA (21x21), 288-FCBGA (23x23), 80-HTQFP (12x12), 548-FCBGA (27x27), 352-FCBGA (35x35), 240-NFBGA (15x15), 38-TSSOP, 388-BGA (35x35), 144-HTQFP (20x20), 100-NFBGA (10x10), 118-BGA MICROSTAR JUNIOR (7x7), 548-FCBGA (23x23), 64-QFP (14x20), 68-PLCC, 288-BGA Microstar (16x16), 201-NFBGA (15x15), 169-BGA MicroStar, 288-NFBGA (16x16), 100-BGA MICROSTAR (10x10), 384-FC/CSP (18x18), 201-BGA MICROSTAR (15x15), 32-LQFP (7x7), 181-CPGA (39x39), 688-FCBGA (23x23), 80-QFP (14x20), 40-PDIP, 208-HLQFP (28x28), 44-PLCC, 68-CPGA (24.38x24.38), 181-CPGA, 143-BGA MICROSTAR JUNIOR (7x7), 340-BGA |

| Supplier Device Package | - | 12 - 40 |

| Supplier Device Package | - | 12 - 40 |

| Type | Floating Point | Digital Media System-on-Chip (DMSoC), Fixed Point, Floating Point, Fixed/Floating Point, DSP+ARM® |

| Voltage - Core | 5 V | 1 - 5 V |

| Voltage - Core | - | Variable |

| Voltage - I/O | 5 V | 1 - 5 V |

| Voltage - Supply (Vcc/Vdd) | - | 1.14 - 4.5 V |

| Voltage - Supply (Vcc/Vdd) | - | 1.26 - 5.5 V |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

TMS320 Series

IC DGTL MEDIA SOC 337NFBGA

| Part | Clock Rate | Operating Temperature [Max] | Operating Temperature [Min] | Voltage - I/O | Voltage - Core | On-Chip RAM | Non-Volatile Memory | Non-Volatile Memory [custom] | Type | Supplier Device Package | Mounting Type | Package / Case | Interface | Program Memory Size | Connectivity | Core Size | Program Memory Type | RAM Size | Oscillator Type | Number of I/O | Speed | Voltage - Supply (Vcc/Vdd) [Min] | Voltage - Supply (Vcc/Vdd) [Max] | Peripherals | Data Converters [custom] | Data Converters [custom] | Core Processor | Non-Volatile Memory | Supplier Device Package [y] | Supplier Device Package [x] | Data Converters [custom] | Data Converters [custom] | Connectivity [custom] | Connectivity [custom] | Connectivity [custom] | Connectivity [custom] | Connectivity [custom] | Connectivity [custom] | Data Converters | Grade | Qualification | Connectivity [custom] | RAM Size | Data Converters [custom] | Data Converters | Clock Rate [custom] | Clock Rate [custom] | Connectivity [custom] | Clock Rate [custom] | Data Converters [custom] | Core Size [custom] | Data Converters [custom] | Data Converters [custom] | Data Converters [custom] | Package / Case | Voltage - Core |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

Texas Instruments TMS320DM355CZCE270 | 270 MHz | 85 °C | 0 °C | 1.8 V, 3.3 V | 1.3 V | 56 kB | ROM | 8 kB | Digital Media System-on-Chip (DMSoC) | 337-BGA (13x13) | Surface Mount | 337-LFBGA | ASP, I2C, SPI, UART, USB | |||||||||||||||||||||||||||||||||||||||||||

Texas Instruments TMS320F28374SPZPSC2000™ 32-bit microcontrollersare optimized for processing, sensing, and actuation to improve closed-loop performance inreal-time control applicationssuch asindustrial motor drives;solar inverters and digital power;electrical vehicles and transportation;motor control; andsensing and signal processing. The C2000 line includes thePremium performance MCUsand theEntry performance MCUs.

The TMS320F2837xS is a powerful 32-bit floating-point microcontroller unit (MCU) designed for advanced closed-loop control applications such asindustrial motor drives;solar inverters and digital power;electrical vehicles and transportation; andsensing and signal processing. To accelerate application development, theDigitalPower software development kit (SDK) for C2000 MCUsand theMotorControl software development kit (SDK) for C2000™ MCUsare available.

The real-time control subsystem is based on TI’s 32-bit C28x floating-point CPU, which provides 200MHz of signal processing performance. The C28x CPU is further boosted by the new TMU accelerator, which enables fast execution of algorithms with trigonometric operations common in transforms and torque loop calculations; and the VCU accelerator, which reduces the time for complex math operations common in encoded applications.

The F2837xS microcontroller family features a CLA real-time control coprocessor. The CLA is an independent 32-bit floating-point processor that runs at the same speed as the main CPU. The CLA responds to peripheral triggers and executes code concurrently with the main C28x CPU. This parallel processing capability can effectively double the computational performance of a real-time control system. By using the CLA to service time-critical functions, the main C28x CPU is free to perform other tasks, such as communications and diagnostics.

The TMS320F2837xS supports up to 1MB (512KW) of onboard flash memory with error correction code (ECC) and up to 164KB (82KW) of SRAM. Two 128-bit secure zones are also available on the CPU for code protection.

Performance analog and control peripherals are also integrated on the F2837xS MCU to further enable system consolidation. Four independent 16-bit ADCs provide precise and efficient management of multiple analog signals, which ultimately boosts system throughput. The new sigma-delta filter module (SDFM) works in conjunction with the sigma-delta modulator to enable isolated current shunt measurements. The Comparator Subsystem (CMPSS) with windowed comparators allows for protection of power stages when current limit conditions are exceeded or not met. Other analog and control peripherals include DACs, PWMs, eCAPs, eQEPs, and other peripherals.

Peripherals such as EMIFs, CAN modules (ISO 11898-1/CAN 2.0B-compliant), and a new uPP interface extend the connectivity of the F2837xS. The uPP interface is a new feature of the C2000™ MCUs and supports high-speed parallel connection to FPGAs or other processors with similar uPP interfaces. Lastly, a USB 2.0 port with MAC and PHY lets users easily add universal serial bus (USB) connectivity to their application.

Want to learn more about features that make C2000 MCUs the right choice for your real-time control system? Check outThe Essential Guide for Developing With C2000™ Real-Time Microcontrollersand visit theC2000™ real-time control MCUspage.

TheGetting Started With C2000™ Real-Time Control Microcontrollers (MCUs) Getting Started Guidecovers all aspects of development with C2000 devices from hardware to support resources. In addition to key reference documents, each section provides relevant links and resources to further expand on the information covered.

Ready to get started? Check out theTMDSCNCD28379DorLAUNCHXL-F28379Devaluation board sand downloadC2000Ware.

To learn more about the C2000 MCUs, visit the C2000 Overview atwww.ti.com/c2000.

C2000™ 32-bit microcontrollersare optimized for processing, sensing, and actuation to improve closed-loop performance inreal-time control applicationssuch asindustrial motor drives;solar inverters and digital power;electrical vehicles and transportation;motor control; andsensing and signal processing. The C2000 line includes thePremium performance MCUsand theEntry performance MCUs.

The TMS320F2837xS is a powerful 32-bit floating-point microcontroller unit (MCU) designed for advanced closed-loop control applications such asindustrial motor drives;solar inverters and digital power;electrical vehicles and transportation; andsensing and signal processing. To accelerate application development, theDigitalPower software development kit (SDK) for C2000 MCUsand theMotorControl software development kit (SDK) for C2000™ MCUsare available.

The real-time control subsystem is based on TI’s 32-bit C28x floating-point CPU, which provides 200MHz of signal processing performance. The C28x CPU is further boosted by the new TMU accelerator, which enables fast execution of algorithms with trigonometric operations common in transforms and torque loop calculations; and the VCU accelerator, which reduces the time for complex math operations common in encoded applications.

The F2837xS microcontroller family features a CLA real-time control coprocessor. The CLA is an independent 32-bit floating-point processor that runs at the same speed as the main CPU. The CLA responds to peripheral triggers and executes code concurrently with the main C28x CPU. This parallel processing capability can effectively double the computational performance of a real-time control system. By using the CLA to service time-critical functions, the main C28x CPU is free to perform other tasks, such as communications and diagnostics.

The TMS320F2837xS supports up to 1MB (512KW) of onboard flash memory with error correction code (ECC) and up to 164KB (82KW) of SRAM. Two 128-bit secure zones are also available on the CPU for code protection.

Performance analog and control peripherals are also integrated on the F2837xS MCU to further enable system consolidation. Four independent 16-bit ADCs provide precise and efficient management of multiple analog signals, which ultimately boosts system throughput. The new sigma-delta filter module (SDFM) works in conjunction with the sigma-delta modulator to enable isolated current shunt measurements. The Comparator Subsystem (CMPSS) with windowed comparators allows for protection of power stages when current limit conditions are exceeded or not met. Other analog and control peripherals include DACs, PWMs, eCAPs, eQEPs, and other peripherals.

Peripherals such as EMIFs, CAN modules (ISO 11898-1/CAN 2.0B-compliant), and a new uPP interface extend the connectivity of the F2837xS. The uPP interface is a new feature of the C2000™ MCUs and supports high-speed parallel connection to FPGAs or other processors with similar uPP interfaces. Lastly, a USB 2.0 port with MAC and PHY lets users easily add universal serial bus (USB) connectivity to their application.

Want to learn more about features that make C2000 MCUs the right choice for your real-time control system? Check outThe Essential Guide for Developing With C2000™ Real-Time Microcontrollersand visit theC2000™ real-time control MCUspage.

TheGetting Started With C2000™ Real-Time Control Microcontrollers (MCUs) Getting Started Guidecovers all aspects of development with C2000 devices from hardware to support resources. In addition to key reference documents, each section provides relevant links and resources to further expand on the information covered.

Ready to get started? Check out theTMDSCNCD28379DorLAUNCHXL-F28379Devaluation board sand downloadC2000Ware.

To learn more about the C2000 MCUs, visit the C2000 Overview atwww.ti.com/c2000. | 125 ¯C | -40 °C | 100-HTQFP (14x14) | Surface Mount | 100-TQFP Exposed Pad | 512 KB | CANbus, I2C, McBSP, SCI, SPI, UART/USART, uPP, USB | 32-Bit Single-Core | FLASH | 66 K | Internal | 41 | 200 MHz | 1.14 V | 3.47 V | DMA, POR, PWM, WDT | D/A 3x12b | A/D 14x12b | C28x | |||||||||||||||||||||||||||||||||||||

Texas Instruments TMS320C6472EZTZA6 | 625 MHz | 100 °C | -40 °C | 1.8 V, 3.3 V | 1.1 V | 1.44 MB | Fixed Point | Surface Mount | 737-BFBGA, FCBGA | Ethernet MAC, Host Interface, I2C, Telecom, UTPOIA | 768 kB | |||||||||||||||||||||||||||||||||||||||||||||

Texas Instruments TMS320C6202GJL200 | 200 MHz | 90 °C | 0 °C | 3.3 V | 1.8 V | 384 kB | External | Fixed Point | 352-FCBGA (27x27) | Surface Mount | 352-BBGA, FCBGA Exposed Pad | McBSP | ||||||||||||||||||||||||||||||||||||||||||||

Texas Instruments TMS320LBC52PZA57 | 57 MHz | 85 °C | -40 °C | 3.3 V | 3.3 V | 2 kB | ROM | 8 kB | Fixed Point | 100-LQFP (14x14) | Surface Mount | 100-LQFP | BSP, SSP | |||||||||||||||||||||||||||||||||||||||||||

Texas Instruments TMS320C5514AZCH10The device is a member of TI's TMS320C5000™ fixed-point Digital Signal Processor (DSP) product family and is designed for low-power applications.

The fixed-point DSP is based on the TMS320C55x™ DSP generation CPU processor core. The C55x™ DSP architecture achieves high performance and low power through increased parallelism and total focus on power savings. The CPU supports an internal bus structure that is composed of one program bus, one 32-bit data read bus and two 16-bit data read buses, two 16-bit data write buses, and additional buses dedicated to peripheral and DMA activity. These buses provide the ability to perform up to four 16-bit data reads and two 16-bit data writes in a single cycle. The device also includes four DMA controllers, each with 4 channels, providing data movement for 16-independent channel contexts without CPU intervention. Each DMA controller can perform one 32-bit data transfer per cycle, in parallel and independent of the CPU activity.

The C55x CPU provides two multiply-accumulate (MAC) units, each capable of 17-bit x 17-bit multiplication and a 32-bit add in a single cycle. A central 40-bit arithmetic/logic unit (ALU) is supported by an additional 16-bit ALU. Use of the ALUs is under instruction set control, providing the ability to optimize parallel activity and power consumption. These resources are managed in the Address Unit (AU) and Data Unit (DU) of the C55x CPU.

The C55x CPU supports a variable byte width instruction set for improved code density. The Instruction Unit (IU) performs 32-bit program fetches from internal or external memory and queues instructions for the Program Unit (PU). The Program Unit decodes the instructions, directs tasks to the Address Unit (AU) and Data Unit (DU) resources, and manages the fully protected pipeline. Predictive branching capability avoids pipeline flushes on execution of conditional instructions.

Serial media is supported through two MultiMedia Card/Secure Digital (MMC/SD) peripherals, four Inter-IC Sound (I2S Bus™) modules, one Serial-Port Interface (SPI) with up to 4 chip selects, one I2C multi-master and slave interface, and a Universal Asynchronous Receiver/Transmitter (UART) interface.

The device peripheral set includes an external memory interface (EMIF) that provides glueless access to asynchronous memories like EPROM, NOR, NAND, and SRAM, as well as to high-speed, high-density memories such as synchronous DRAM (SDRAM) and mobile SDRAM (mSDRAM). Additional peripherals include: a high-speed Universal Serial Bus (USB2.0) device mode only, and a real-time clock (RTC). This device also includes three general-purpose timers with one configurable as a watchdog timer, and an analog phase-locked loop (APLL) clock generator.

Furthermore, the device includes three integrated LDOs (DSP_LDO, ANA_LDO, and USB_LDO) to power different sections of the device. The DSP_LDO can provide 1.3 V or 1.05 V to the DSP core (CVDD), selectable on-the-fly by software as long as operating frequency ranges are observed. To allow for lowest power operation, the programmer can shutdown the internal DSP_LDO cutting power to the DSP core (CVDD) while an external supply provides power to the RTC (CVDDRTCand DVDDRTC). The ANA_LDO is designed to provide 1.3 V to the DSP PLL (VDDA_PLL) and power management circuits (VDDA_ANA). The USB_LDO provides 1.3 V to USB core digital (USB_VDD1P3) and PHY circuits (USB_VDDA1P3). The RTC alarm interrupt or the WAKEUP pin can re-enable the internal DSP_LDO and re-apply power to the DSP core.

The device is supported by the industry’s award-winning eXpressDSP™, Code Composer Studio™ Integrated Development Environment (IDE), DSP/BIOS™, Texas Instruments’ algorithm standard, and the industry’s largest third-party network. Code Composer Studio IDE features code generation tools including a C Compiler and Linker, RTDX™, XDS100™, XDS510™, XDS560™ emulation device drivers, and evaluation modules. The device is also supported by the C55x DSP Library which features more than 50 foundational software kernels (FIR filters, IIR filters, and various math functions) as well as chip support libraries.

The device is a member of TI's TMS320C5000™ fixed-point Digital Signal Processor (DSP) product family and is designed for low-power applications.

The fixed-point DSP is based on the TMS320C55x™ DSP generation CPU processor core. The C55x™ DSP architecture achieves high performance and low power through increased parallelism and total focus on power savings. The CPU supports an internal bus structure that is composed of one program bus, one 32-bit data read bus and two 16-bit data read buses, two 16-bit data write buses, and additional buses dedicated to peripheral and DMA activity. These buses provide the ability to perform up to four 16-bit data reads and two 16-bit data writes in a single cycle. The device also includes four DMA controllers, each with 4 channels, providing data movement for 16-independent channel contexts without CPU intervention. Each DMA controller can perform one 32-bit data transfer per cycle, in parallel and independent of the CPU activity.

The C55x CPU provides two multiply-accumulate (MAC) units, each capable of 17-bit x 17-bit multiplication and a 32-bit add in a single cycle. A central 40-bit arithmetic/logic unit (ALU) is supported by an additional 16-bit ALU. Use of the ALUs is under instruction set control, providing the ability to optimize parallel activity and power consumption. These resources are managed in the Address Unit (AU) and Data Unit (DU) of the C55x CPU.

The C55x CPU supports a variable byte width instruction set for improved code density. The Instruction Unit (IU) performs 32-bit program fetches from internal or external memory and queues instructions for the Program Unit (PU). The Program Unit decodes the instructions, directs tasks to the Address Unit (AU) and Data Unit (DU) resources, and manages the fully protected pipeline. Predictive branching capability avoids pipeline flushes on execution of conditional instructions.

Serial media is supported through two MultiMedia Card/Secure Digital (MMC/SD) peripherals, four Inter-IC Sound (I2S Bus™) modules, one Serial-Port Interface (SPI) with up to 4 chip selects, one I2C multi-master and slave interface, and a Universal Asynchronous Receiver/Transmitter (UART) interface.

The device peripheral set includes an external memory interface (EMIF) that provides glueless access to asynchronous memories like EPROM, NOR, NAND, and SRAM, as well as to high-speed, high-density memories such as synchronous DRAM (SDRAM) and mobile SDRAM (mSDRAM). Additional peripherals include: a high-speed Universal Serial Bus (USB2.0) device mode only, and a real-time clock (RTC). This device also includes three general-purpose timers with one configurable as a watchdog timer, and an analog phase-locked loop (APLL) clock generator.

Furthermore, the device includes three integrated LDOs (DSP_LDO, ANA_LDO, and USB_LDO) to power different sections of the device. The DSP_LDO can provide 1.3 V or 1.05 V to the DSP core (CVDD), selectable on-the-fly by software as long as operating frequency ranges are observed. To allow for lowest power operation, the programmer can shutdown the internal DSP_LDO cutting power to the DSP core (CVDD) while an external supply provides power to the RTC (CVDDRTCand DVDDRTC). The ANA_LDO is designed to provide 1.3 V to the DSP PLL (VDDA_PLL) and power management circuits (VDDA_ANA). The USB_LDO provides 1.3 V to USB core digital (USB_VDD1P3) and PHY circuits (USB_VDDA1P3). The RTC alarm interrupt or the WAKEUP pin can re-enable the internal DSP_LDO and re-apply power to the DSP core.

The device is supported by the industry’s award-winning eXpressDSP™, Code Composer Studio™ Integrated Development Environment (IDE), DSP/BIOS™, Texas Instruments’ algorithm standard, and the industry’s largest third-party network. Code Composer Studio IDE features code generation tools including a C Compiler and Linker, RTDX™, XDS100™, XDS510™, XDS560™ emulation device drivers, and evaluation modules. The device is also supported by the C55x DSP Library which features more than 50 foundational software kernels (FIR filters, IIR filters, and various math functions) as well as chip support libraries. | 100 MHz | 70 °C | -10 °C | 1.8 V, 2.5 V, 2.8 V, 3.3 V | 1.3 V | 2 Mbit | Fixed Point | 196-NFBGA (10x10) | Surface Mount | 196-LFBGA | EBI/EMI, I2C, I2S, MMC/SD, SPI, UART/USART, USB | 128 kB | ||||||||||||||||||||||||||||||||||||||||||||

Texas Instruments TMS320C44PDB60 | 60 MHz | 85 °C | 0 °C | 5 V | 5 V | 8 kB | External | Floating Point | 304-PQFP | Surface Mount | 304-BFQFP Exposed Pad | Communication Ports | 40 | 40 | ||||||||||||||||||||||||||||||||||||||||||

Texas Instruments TMS320C80GF50 | 50 MHz | 85 °C | 0 °C | 3.3 V | 3.3 V | 98 kB | External | Floating Point | 305-CPGA (47.25x47.25) | Through Hole | 305-BFCPGA Exposed Pad | Parallel | ||||||||||||||||||||||||||||||||||||||||||||

Texas Instruments TMS320LC542PBK1-50 | 50 MHz | 100 °C | -40 °C | 3.3 V | 3.3 V | 20 kB | Fixed Point | 128-LQFP (14x14) | Surface Mount | 128-LQFP | BSP, HPI, TDM | |||||||||||||||||||||||||||||||||||||||||||||

Texas Instruments TMS320F28069FPNTC2000™ 32-bit microcontrollersare optimized for processing, sensing, and actuation to improve closed-loop performance inreal-time control applicationssuch asindustrial motor drives;solar inverters and digital power;electrical vehicles and transportation;motor control; andsensing and signal processing. The C2000 line includes thePremium performance MCUsand theEntry performance MCUs.

The F2806x family of microcontrollers (MCUs) provides the power of the C28x core and CLA coupled with highly integrated control peripherals in low pin-count devices. This family is code-compatible with previous C28x-based code, and also provides a high level of analog integration.

An internal voltage regulator allows for single-rail operation. Enhancements have been made to the HRPWM module to allow for dual-edge control (frequency modulation). Analog comparators with internal 10-bit references have been added and can be routed directly to control the ePWM outputs. The ADC converts from 0 to 3.3-V fixed full-scale range and supports ratio-metric VREFHI/VREFLOreferences. The ADC interface has been optimized for low overhead and latency.

To learn more about the C2000 MCUs, visit the C2000 Overview atwww.ti.com/c2000.

C2000™ 32-bit microcontrollersare optimized for processing, sensing, and actuation to improve closed-loop performance inreal-time control applicationssuch asindustrial motor drives;solar inverters and digital power;electrical vehicles and transportation;motor control; andsensing and signal processing. The C2000 line includes thePremium performance MCUsand theEntry performance MCUs.

The F2806x family of microcontrollers (MCUs) provides the power of the C28x core and CLA coupled with highly integrated control peripherals in low pin-count devices. This family is code-compatible with previous C28x-based code, and also provides a high level of analog integration.

An internal voltage regulator allows for single-rail operation. Enhancements have been made to the HRPWM module to allow for dual-edge control (frequency modulation). Analog comparators with internal 10-bit references have been added and can be routed directly to control the ePWM outputs. The ADC converts from 0 to 3.3-V fixed full-scale range and supports ratio-metric VREFHI/VREFLOreferences. The ADC interface has been optimized for low overhead and latency.

To learn more about the C2000 MCUs, visit the C2000 Overview atwww.ti.com/c2000. | 105 °C | -40 °C | Surface Mount | 80-LQFP | 256 KB | 32-Bit Single-Core | FLASH | Internal | 40 | 90 MHz | 1.71 V | 1.995 V | Brown-out Detect/Reset, DMA, POR, PWM, WDT | C28x | 12 bits | 12 | CANbus | UART/USART | SCI | SPI | I2C | McBSP | ||||||||||||||||||||||||||||||||||

Texas Instruments TMS320C54CSTPGEThe 54CST are based on an advanced modified Harvard architecture that has one program memory bus and three data memory buses. These processors provide an arithmetic logic unit (ALU) with a high degree of parallelism, application-specific hardware logic, on-chip memory, and additional on-chip peripherals. The basis of the operational flexibility and speed of these DSPs is a highly specialized instruction set.

Separate program and data spaces allow simultaneous access to program instructions and data, providing a high degree of parallelism. Two read operations and one write operation can be performed in a single cycle. Instructions with parallel store and application-specific instructions can fully utilize this architecture. In addition, data can be transferred between data and program spaces. Such parallelism supports a powerful set of arithmetic, logic, and bit-manipulation operations that can all be performed in a single machine cycle. These DSPs also include the control mechanisms to manage interrupts, repeated operations, and function calls.

The 54CST are based on an advanced modified Harvard architecture that has one program memory bus and three data memory buses. These processors provide an arithmetic logic unit (ALU) with a high degree of parallelism, application-specific hardware logic, on-chip memory, and additional on-chip peripherals. The basis of the operational flexibility and speed of these DSPs is a highly specialized instruction set.

Separate program and data spaces allow simultaneous access to program instructions and data, providing a high degree of parallelism. Two read operations and one write operation can be performed in a single cycle. Instructions with parallel store and application-specific instructions can fully utilize this architecture. In addition, data can be transferred between data and program spaces. Such parallelism supports a powerful set of arithmetic, logic, and bit-manipulation operations that can all be performed in a single machine cycle. These DSPs also include the control mechanisms to manage interrupts, repeated operations, and function calls. | 120 MHz | 100 °C | 0 °C | 3.3 V | 1.5 V | 80 kB | Fixed Point | 144-LQFP (20x20) | Surface Mount | 144-LQFP | Host Interface, McBSP, UART | 256 kB | ||||||||||||||||||||||||||||||||||||||||||||

Texas Instruments TMS320VC5441APGF | 133 MHz | 100 °C | -40 °C | 3.3 V | 1.6 V | 1.25 MB | External | Fixed Point | 176-LQFP (24x24) | Surface Mount | 176-LQFP | Host Interface, McBSP | ||||||||||||||||||||||||||||||||||||||||||||

Texas Instruments TMS320C6414TBCLZ1The TMS320C64x™ DSPs (including the TMS320C6414T, TMS320C6415T, and TMS320C6416T devices) are the highest-performance fixed-point DSP generation in the TMS320C6000™ DSP platform. The TMS320C64x™ (C64x™) device is based on the second-generation high-performance, advanced VelociTI™ very-long-instruction-word (VLIW) architecture (VelociTI.2™) developed by Texas Instruments (TI), making these DSPs an excellent choice for wireless infrastructure applications. The C64x™ is a code-compatible member of the C6000™ DSP platform.

With performance of up to 8000 million instructions per second (MIPS) at a clock rate of 1 GHz, the C64x devices offer cost-effective solutions to high-performance DSP programming challenges. The C64x™ DSPs possess the operational flexibility of high-speed controllers and the numerical capability of array processors. The C64x. DSP core processor has 64 general-purpose registers of 32-bit word length and eight highly independent functional units—two multipliers for a 32-bit result and six arithmetic logic units (ALUs)— with VelociTI.2™ extensions. The VelociTI.2™ extensions in the eight functional units include new instructions to accelerate the performance in key applications and extend the parallelism of the VelociTI™ architecture. The C64x can produce four 16-bit multiply-accumulates (MACs) per cycle for a total of 4000 million MACs per second (MMACS), or eight 8-bit MACs per cycle for a total of 8000 MMACS. The C64x DSP also has application-specific hardware logic, on-chip memory, and additional on-chip peripherals similar to the other C6000™ DSP platform devices.

The C6416T device has two high-performance embedded coprocessors [Viterbi Decoder Coprocessor (VCP) and Turbo Decoder Coprocessor (TCP)] that significantly speed up channel-decoding operations on-chip. The VCP operating at CPU clock divided-by-4 can decode over 833 7.95-Kbps adaptive multi-rate (AMR) [K = 9, R = 1/3] voice channels. The VCP supports constraint lengths K = 5, 6, 7, 8, and 9, rates R = 1/2, 1/3, and 1/4, and flexible polynomials, while generating hard decisions or soft decisions. The TCP operating at CPU clock divided-by-2 can decode up to sixty 384-Kbps or ten 2-Mbps turbo encoded channels (assuming 6 iterations). The TCP implements the max*log-map algorithm and is designed to support all polynomials and rates required by Third-Generation Partnership Projects (3GPP and 3GPP2), with fully programmable frame length and turbo interleaver. Decoding parameters such as the number of iterations and stopping criteria are also programmable. Communications between the VCP/TCP and the CPU are carried out through the EDMA controller.

The C64x uses a two-level cache-based architecture and has a powerful and diverse set of peripherals. The Level 1 program cache (L1P) is a 128-Kbit direct mapped cache and the Level 1 data cache (L1D) is a 128-Kbit 2-way set-associative cache. The Level 2 memory/cache (L2) consists of an 8-Mbit memory space that is shared between program and data space. L2 memory can be configured as mapped memory or combinations of cache (up to 256K bytes) and mapped memory. The peripheral set includes three multichannel buffered serial ports (McBSPs); an 8-bit Universal Test and Operations PHY Interface for Asynchronous Transfer Mode (ATM) Slave [UTOPIA Slave] port [C6415T/C6416T only]; three 32-bit general-purpose timers; a user-configurable 16-bit or 32-bit host-port interface (HPI16/HPI32); a peripheral component interconnect (PCI) [C6415T/C6416T only]; a general-purpose input/output port (GPIO) with 16 GPIO pins; and two glueless external memory interfaces (64-bit EMIFA and 16-bit EMIFB), both of which are capable of interfacing to synchronous and asynchronous memories and peripherals.

The C64x has a complete set of development tools which includes: an advanced C compiler with C64x-specific enhancements, an assembly optimizer to simplify programming and scheduling, and a Windows. debugger interface for visibility into source code execution.

TMS320C6000, C64x, and C6000 are trademarks of Texas Instruments.Windows is a registered trademark of the Microsoft Corporation.Other trademarks are the property of their respective owners.Throughout the remainder of this document, the TMS320C6414T, TMS320C6415T, and TMS320C6416T shall be referred to as TMS320C64x or C64x where generic, and where specific, their individual full device part numbers will be used or abbreviated as C6414T, C6415T, or C6416T.These C64x™ devices have two EMIFs (64-bit EMIFA and 16-bit EMIFB). The prefix "A" in front of a signal name indicates it is an EMIFA signal whereas a prefix "B" in front of a signal name indicates it is an EMIFB signal. Throughout the rest of this document, in generic EMIF areas of discussion, the prefix "A" or "B" may be omitted from the signal name.

The TMS320C64x™ DSPs (including the TMS320C6414T, TMS320C6415T, and TMS320C6416T devices) are the highest-performance fixed-point DSP generation in the TMS320C6000™ DSP platform. The TMS320C64x™ (C64x™) device is based on the second-generation high-performance, advanced VelociTI™ very-long-instruction-word (VLIW) architecture (VelociTI.2™) developed by Texas Instruments (TI), making these DSPs an excellent choice for wireless infrastructure applications. The C64x™ is a code-compatible member of the C6000™ DSP platform.

With performance of up to 8000 million instructions per second (MIPS) at a clock rate of 1 GHz, the C64x devices offer cost-effective solutions to high-performance DSP programming challenges. The C64x™ DSPs possess the operational flexibility of high-speed controllers and the numerical capability of array processors. The C64x. DSP core processor has 64 general-purpose registers of 32-bit word length and eight highly independent functional units—two multipliers for a 32-bit result and six arithmetic logic units (ALUs)— with VelociTI.2™ extensions. The VelociTI.2™ extensions in the eight functional units include new instructions to accelerate the performance in key applications and extend the parallelism of the VelociTI™ architecture. The C64x can produce four 16-bit multiply-accumulates (MACs) per cycle for a total of 4000 million MACs per second (MMACS), or eight 8-bit MACs per cycle for a total of 8000 MMACS. The C64x DSP also has application-specific hardware logic, on-chip memory, and additional on-chip peripherals similar to the other C6000™ DSP platform devices.

The C6416T device has two high-performance embedded coprocessors [Viterbi Decoder Coprocessor (VCP) and Turbo Decoder Coprocessor (TCP)] that significantly speed up channel-decoding operations on-chip. The VCP operating at CPU clock divided-by-4 can decode over 833 7.95-Kbps adaptive multi-rate (AMR) [K = 9, R = 1/3] voice channels. The VCP supports constraint lengths K = 5, 6, 7, 8, and 9, rates R = 1/2, 1/3, and 1/4, and flexible polynomials, while generating hard decisions or soft decisions. The TCP operating at CPU clock divided-by-2 can decode up to sixty 384-Kbps or ten 2-Mbps turbo encoded channels (assuming 6 iterations). The TCP implements the max*log-map algorithm and is designed to support all polynomials and rates required by Third-Generation Partnership Projects (3GPP and 3GPP2), with fully programmable frame length and turbo interleaver. Decoding parameters such as the number of iterations and stopping criteria are also programmable. Communications between the VCP/TCP and the CPU are carried out through the EDMA controller.

The C64x uses a two-level cache-based architecture and has a powerful and diverse set of peripherals. The Level 1 program cache (L1P) is a 128-Kbit direct mapped cache and the Level 1 data cache (L1D) is a 128-Kbit 2-way set-associative cache. The Level 2 memory/cache (L2) consists of an 8-Mbit memory space that is shared between program and data space. L2 memory can be configured as mapped memory or combinations of cache (up to 256K bytes) and mapped memory. The peripheral set includes three multichannel buffered serial ports (McBSPs); an 8-bit Universal Test and Operations PHY Interface for Asynchronous Transfer Mode (ATM) Slave [UTOPIA Slave] port [C6415T/C6416T only]; three 32-bit general-purpose timers; a user-configurable 16-bit or 32-bit host-port interface (HPI16/HPI32); a peripheral component interconnect (PCI) [C6415T/C6416T only]; a general-purpose input/output port (GPIO) with 16 GPIO pins; and two glueless external memory interfaces (64-bit EMIFA and 16-bit EMIFB), both of which are capable of interfacing to synchronous and asynchronous memories and peripherals.

The C64x has a complete set of development tools which includes: an advanced C compiler with C64x-specific enhancements, an assembly optimizer to simplify programming and scheduling, and a Windows. debugger interface for visibility into source code execution.

TMS320C6000, C64x, and C6000 are trademarks of Texas Instruments.Windows is a registered trademark of the Microsoft Corporation.Other trademarks are the property of their respective owners.Throughout the remainder of this document, the TMS320C6414T, TMS320C6415T, and TMS320C6416T shall be referred to as TMS320C64x or C64x where generic, and where specific, their individual full device part numbers will be used or abbreviated as C6414T, C6415T, or C6416T.These C64x™ devices have two EMIFs (64-bit EMIFA and 16-bit EMIFB). The prefix "A" in front of a signal name indicates it is an EMIFA signal whereas a prefix "B" in front of a signal name indicates it is an EMIFB signal. Throughout the rest of this document, in generic EMIF areas of discussion, the prefix "A" or "B" may be omitted from the signal name. | 90 °C | 0 °C | 3.3 V | 1.1 V | 1.03 MB | External | Fixed Point | 532-FC/CSP (23x23) | Surface Mount | 532-BFBGA, FCBGA | Host Interface, McBSP, PCI, UTOPIA | |||||||||||||||||||||||||||||||||||||||||||||

Texas Instruments TMS320DM6435ZWT6The TMS320C64x+™ DSPs (including the TMS320DM6435 device) are the highest-performance fixed-point DSP generation in the TMS320C6000™ DSP platform. The DM6435 device is based on the third-generation high-performance, advanced VelociTI™ very-long-instruction-word (VLIW) architecture developed by Texas Instruments (TI), making these DSPs an excellent choice for digital media applications. The C64x+™ devices are upward code-compatible from previous devices that are part of the C6000™ DSP platform. The C64x™ DSPs support added functionality and have an expanded instruction set from previous devices.

Any reference to the C64x DSP or C64x CPU also applies, unless otherwise noted, to the C64x+ DSP and C64x+ CPU, respectively.

With performance of up to 4800 million instructions per second (MIPS) at a clock rate of 600 MHz, the C64x+ core offers solutions to high-performance DSP programming challenges. The DSP core possesses the operational flexibility of high-speed controllers and the numerical capability of array processors. The C64x+ DSP core processor has 64 general-purpose registers of 32-bit word length and eight highly independent functional units–two multipliers for a 32-bit result and six arithmetic logic units (ALUs). The eight functional units include instructions to accelerate the performance in video and imaging applications. The DSP core can produce four 16-bit multiply-accumulates (MACs) per cycle for a total of 2400 million MACs per second (MMACS), or eight 8-bit MACs per cycle for a total of 4800 MMACS. For more details on the C64x+ DSP, see the TMS320C64x/C64x+ DSP CPU and Instruction Set Reference Guide (literature number SPRU732).

The DM6435 also has application-specific hardware logic, on-chip memory, and additional on-chip peripherals similar to the other C6000 DSP platform devices. The DM6435 core uses a two-level cache-based architecture. The Level 1 program memory/cache (L1P) consists of a 256K-bit memory space that can be configured as mapped memory or direct mapped cache, and the Level 1 data (L1D) consists of a 640K-bit memory space–384K-bit of which is mapped memory and 256K-bit of which can be configured as mapped memory or 2-way set-associative cache. The Level 2 memory/cache (L2) consists of a 1M-bit memory space that is shared between program and data space. L2 memory can be configured as mapped memory, cache, or combinations of the two.

The peripheral set includes: a configurable video port (VPFE); a 10/100 Mb/s Ethernet MAC (EMAC) with a management data input/output (MDIO) module; a 4-bit transmit, 4-bit receive VLYNQ interface; an inter-integrated circuit (I2C) Bus interface; a multichannel buffered serial port (McBSP); a multichannel audio serial port (McASP0) with 4 serializers; 2 64-bit general-purpose timers each configurable as 2 independent 32-bit timers; 1 64-bit watchdog timer; a user-configurable 16-bit host-port interface (HPI); up to 111-pins of general-purpose input/output (GPIO) with programmable interrupt/event generation modes, multiplexed with other peripherals; 2 UARTs with hardware handshaking support on 1 UART; 3 pulse width modulator (PWM) peripherals; 1 high-end controller area network (CAN) controller [HECC]; and 2 glueless external memory interfaces: an asynchronous external memory interface (EMIFA) for slower memories/peripherals, and a higher speed synchronous memory interface for DDR2.

The DM6435 device includes a Video Processing Subsystem (VPSS) with a configurable video/imaging front-end input peripheral used for video capture.

The Video Processing Front-End (VPFE) is comprised of a CCD Controller (CCDC), a Preview Engine (Previewer), Histogram Module, Auto-Exposure/White Balance/Focus Module (H3A), and Resizer. The CCDC is capable of interfacing to common video decoders, CMOS sensors, and Charge Coupled Devices (CCDs). The Previewer is a real-time image processing engine that takes raw imager data from a CMOS sensor or CCD and converts from an RGB Bayer Pattern to YUV422. The Histogram and H3A modules provide statistical information on the raw color data for use by the DM6435. The Resizer accepts image data for separate horizontal and vertical resizing from 1/4x to 4x in increments of 256/N, where N is between 64 and 1024.

The Ethernet Media Access Controller (EMAC) provides an efficient interface between the DM6435 and the network. The DM6435 EMAC support both 10Base-T and 100Base-TX, or 10 Mbits/second (Mbps) and 100 Mbps in either half- or full-duplex mode, with hardware flow control and quality of service (QOS) support.

The Management Data Input/Output (MDIO) module continuously polls all 32 MDIO addresses in order to enumerate all PHY devices in the system.

The I2C and VLYNQ ports allow DM6435 to easily control peripheral devices and/or communicate with host processors.

The high-end controller area network (CAN) controller [HECC] module provides a network protocol in a harsh environment to communicate serially with other controllers, typically in automotive applications.

The rich peripheral set provides the ability to control external peripheral devices and communicate with external processors. For details on each of the peripherals, see the related sections later in this document and the associated peripheral reference guides.

The DM6435 has a complete set of development tools. These include C compilers, a DSP assembly optimizer to simplify programming and scheduling, and a Windows™ debugger interface for visibility into source code execution.

The TMS320C64x+™ DSPs (including the TMS320DM6435 device) are the highest-performance fixed-point DSP generation in the TMS320C6000™ DSP platform. The DM6435 device is based on the third-generation high-performance, advanced VelociTI™ very-long-instruction-word (VLIW) architecture developed by Texas Instruments (TI), making these DSPs an excellent choice for digital media applications. The C64x+™ devices are upward code-compatible from previous devices that are part of the C6000™ DSP platform. The C64x™ DSPs support added functionality and have an expanded instruction set from previous devices.

Any reference to the C64x DSP or C64x CPU also applies, unless otherwise noted, to the C64x+ DSP and C64x+ CPU, respectively.

With performance of up to 4800 million instructions per second (MIPS) at a clock rate of 600 MHz, the C64x+ core offers solutions to high-performance DSP programming challenges. The DSP core possesses the operational flexibility of high-speed controllers and the numerical capability of array processors. The C64x+ DSP core processor has 64 general-purpose registers of 32-bit word length and eight highly independent functional units–two multipliers for a 32-bit result and six arithmetic logic units (ALUs). The eight functional units include instructions to accelerate the performance in video and imaging applications. The DSP core can produce four 16-bit multiply-accumulates (MACs) per cycle for a total of 2400 million MACs per second (MMACS), or eight 8-bit MACs per cycle for a total of 4800 MMACS. For more details on the C64x+ DSP, see the TMS320C64x/C64x+ DSP CPU and Instruction Set Reference Guide (literature number SPRU732).

The DM6435 also has application-specific hardware logic, on-chip memory, and additional on-chip peripherals similar to the other C6000 DSP platform devices. The DM6435 core uses a two-level cache-based architecture. The Level 1 program memory/cache (L1P) consists of a 256K-bit memory space that can be configured as mapped memory or direct mapped cache, and the Level 1 data (L1D) consists of a 640K-bit memory space–384K-bit of which is mapped memory and 256K-bit of which can be configured as mapped memory or 2-way set-associative cache. The Level 2 memory/cache (L2) consists of a 1M-bit memory space that is shared between program and data space. L2 memory can be configured as mapped memory, cache, or combinations of the two.

The peripheral set includes: a configurable video port (VPFE); a 10/100 Mb/s Ethernet MAC (EMAC) with a management data input/output (MDIO) module; a 4-bit transmit, 4-bit receive VLYNQ interface; an inter-integrated circuit (I2C) Bus interface; a multichannel buffered serial port (McBSP); a multichannel audio serial port (McASP0) with 4 serializers; 2 64-bit general-purpose timers each configurable as 2 independent 32-bit timers; 1 64-bit watchdog timer; a user-configurable 16-bit host-port interface (HPI); up to 111-pins of general-purpose input/output (GPIO) with programmable interrupt/event generation modes, multiplexed with other peripherals; 2 UARTs with hardware handshaking support on 1 UART; 3 pulse width modulator (PWM) peripherals; 1 high-end controller area network (CAN) controller [HECC]; and 2 glueless external memory interfaces: an asynchronous external memory interface (EMIFA) for slower memories/peripherals, and a higher speed synchronous memory interface for DDR2.

The DM6435 device includes a Video Processing Subsystem (VPSS) with a configurable video/imaging front-end input peripheral used for video capture.

The Video Processing Front-End (VPFE) is comprised of a CCD Controller (CCDC), a Preview Engine (Previewer), Histogram Module, Auto-Exposure/White Balance/Focus Module (H3A), and Resizer. The CCDC is capable of interfacing to common video decoders, CMOS sensors, and Charge Coupled Devices (CCDs). The Previewer is a real-time image processing engine that takes raw imager data from a CMOS sensor or CCD and converts from an RGB Bayer Pattern to YUV422. The Histogram and H3A modules provide statistical information on the raw color data for use by the DM6435. The Resizer accepts image data for separate horizontal and vertical resizing from 1/4x to 4x in increments of 256/N, where N is between 64 and 1024.

The Ethernet Media Access Controller (EMAC) provides an efficient interface between the DM6435 and the network. The DM6435 EMAC support both 10Base-T and 100Base-TX, or 10 Mbits/second (Mbps) and 100 Mbps in either half- or full-duplex mode, with hardware flow control and quality of service (QOS) support.

The Management Data Input/Output (MDIO) module continuously polls all 32 MDIO addresses in order to enumerate all PHY devices in the system.

The I2C and VLYNQ ports allow DM6435 to easily control peripheral devices and/or communicate with host processors.

The high-end controller area network (CAN) controller [HECC] module provides a network protocol in a harsh environment to communicate serially with other controllers, typically in automotive applications.

The rich peripheral set provides the ability to control external peripheral devices and communicate with external processors. For details on each of the peripherals, see the related sections later in this document and the associated peripheral reference guides.

The DM6435 has a complete set of development tools. These include C compilers, a DSP assembly optimizer to simplify programming and scheduling, and a Windows™ debugger interface for visibility into source code execution. | 600 MHz | 90 °C | 0 °C | 1.8 V, 3.3 V | 1.05 V, 1.2 V | 240 kB | Fixed Point | 361-NFBGA (16x16) | Surface Mount | 361-LFBGA | 10/100 Ethernet MAC, HPI, I2C, McASP, McBSP, UART | 64 kB | ||||||||||||||||||||||||||||||||||||||||||||

Texas Instruments TMS320C28341ZAYTThe TMS320C2834x (C2834x) Delfino™ microcontroller unit (MCU) devices build on TI’s existing F2833x high-performance floating-point microcontrollers. The C2834x delivers up to 300 MHz of floating-point performance, and has up to 516KB of on-chip RAM. Designed for real-time control applications, the C2834x is based on the C28x core, making it code-compatible with all C28x microcontrollers. The on-chip peripherals and low-latency core make the C2834x an excellent solution for performance-hungry real-time control applications.

The TMS320C28346, TMS320C28345, TMS320C28344, TMS320C28343, TMS320C28342, and TMS320C28341 devices, members of the Delfino™ MCU generation, are highly integrated, high-performance solutions for demanding control applications.

Throughout this document, the devices are abbreviated as C28346, C28345, C28344, C28343, C28342, and C28341, respectively. Device Comparison provides a summary of features for each device.

The TMS320C2834x (C2834x) Delfino™ microcontroller unit (MCU) devices build on TI’s existing F2833x high-performance floating-point microcontrollers. The C2834x delivers up to 300 MHz of floating-point performance, and has up to 516KB of on-chip RAM. Designed for real-time control applications, the C2834x is based on the C28x core, making it code-compatible with all C28x microcontrollers. The on-chip peripherals and low-latency core make the C2834x an excellent solution for performance-hungry real-time control applications.

The TMS320C28346, TMS320C28345, TMS320C28344, TMS320C28343, TMS320C28342, and TMS320C28341 devices, members of the Delfino™ MCU generation, are highly integrated, high-performance solutions for demanding control applications.

Throughout this document, the devices are abbreviated as C28346, C28345, C28344, C28343, C28342, and C28341, respectively. Device Comparison provides a summary of features for each device. | 200 MHz | 105 °C | -40 °C | 3.3 V | 1.1 V | 196 kB | Floating Point | 179-NFBGA (12x12) | Surface Mount | CAN, EBI/EMI, I2C, McBSP, SCI, SPI | 16 kB | |||||||||||||||||||||||||||||||||||||||||||||

Texas Instruments TMS320F28052MPNQC2000™ real-time control MCUsare optimized for processing, sensing, and actuation to improve closed-loop performance inreal-time control applicationssuch asindustrial motor drives;solar inverters and digital power;electrical vehicles and transportation;motor control; andsensing and signal processing. The C2000 line includes thePremium performance MCUsand theEntry performance MCUs.

The F2805x family of microcontrollers (MCUs) provides the power of the C28x core and CLA coupled with highly integrated control peripherals in low pin-count devices. This family is code-compatible with previous C28x-based code, and also provides a high level of analog integration.

An internal voltage regulator allows for single-rail operation. Analog comparators with internal 6-bit references have been added and can be routed directly to control the PWM outputs. The ADC converts from 0 to 3.3-V fixed full-scale range and supports ratio-metric VREFHI/VREFLOreferences. The ADC interface has been optimized for low overhead and latency.

The Analog Front End (AFE) contains up to seven comparators with up to three integrated DACs, one VREFOUT-buffered DAC, up to four PGAs, and up to four digital filters. The PGAs can amplify the input signal in three discrete gain modes. The actual number of AFE peripherals will depend upon the TMS320F2805x device number. See Device Comparison for more details.

To learn more about the C2000 MCUs, visit theC2000™ real-time control MCUspage.

C2000™ real-time control MCUsare optimized for processing, sensing, and actuation to improve closed-loop performance inreal-time control applicationssuch asindustrial motor drives;solar inverters and digital power;electrical vehicles and transportation;motor control; andsensing and signal processing. The C2000 line includes thePremium performance MCUsand theEntry performance MCUs.

The F2805x family of microcontrollers (MCUs) provides the power of the C28x core and CLA coupled with highly integrated control peripherals in low pin-count devices. This family is code-compatible with previous C28x-based code, and also provides a high level of analog integration.

An internal voltage regulator allows for single-rail operation. Analog comparators with internal 6-bit references have been added and can be routed directly to control the PWM outputs. The ADC converts from 0 to 3.3-V fixed full-scale range and supports ratio-metric VREFHI/VREFLOreferences. The ADC interface has been optimized for low overhead and latency.

The Analog Front End (AFE) contains up to seven comparators with up to three integrated DACs, one VREFOUT-buffered DAC, up to four PGAs, and up to four digital filters. The PGAs can amplify the input signal in three discrete gain modes. The actual number of AFE peripherals will depend upon the TMS320F2805x device number. See Device Comparison for more details.

To learn more about the C2000 MCUs, visit theC2000™ real-time control MCUspage. | 125 °C | -40 °C | Surface Mount | 80-LQFP | 64 KB | 32-Bit Single-Core | FLASH | 8 K | Internal | 60 MHz | 1.71 V | 1.995 V | C28x | 12 b, 16 | Automotive | AEC-Q100 | CANbus, I2C, SCI, SPI, UART/USART | |||||||||||||||||||||||||||||||||||||||

Texas Instruments TMS320C6454BZTZ | 90 °C | 0 °C | 1.2 V, 1.5 V, 1.8 V, 3.3 V | 1.25 V | 1.08 MB | ROM | Fixed Point | 697-FCBGA (24x24) | Surface Mount | 697-BFBGA, FCBGA | 10/100/1000 Ethernet MAC, Host Interface, I2C, McBSP, PCI | 32 kB | ||||||||||||||||||||||||||||||||||||||||||||

Texas Instruments TMS320DM8127SCYED3TMS320DM8127 DaVinci Digital Media processors are highly integrated, programmable platforms that leverage the technology to meet the processing needs of the following applications to name a few:IP Network Cameras Industrial Automation Network Cameras Stereo Cameras Video Surveillance HD Video Conferencing Car Black BoxHome Audio and Video Equipment

The device enables Original-Equipment Manufacturers (OEMs) and Original-Design Manufacturers (ODMs) to quickly bring to market devices featuring robust operating systems support, rich user interfaces, and high processing performance through the maximum flexibility of a fully integrated mixed processor solution. The device also combines programmable video and audio processing with a highly integrated peripheral set.

Programmability is provided by an ARM Cortex-A8 RISC CPU with Neon extension, TI C674x VLIW floating-point DSP core, and high-definition video and imaging coprocessors. The ARM lets developers keep control functions separate from A/V algorithms programmed on the DSP and coprocessors, thus reducing the complexity of the system software. The ARM Cortex-A8 32-Bit RISC Core with Neon floating-point extension includes: 32KB of Instruction cache; 32KB of Data cache; 256KB of L2 Cache; 48KB of Boot ROM; and 64KB of RAM.

The rich peripheral set provides the ability to control external peripheral devices and communicate with external processors. For details on each of the peripherals, see the related sections in this document and the associated peripheral reference guides. The peripheral set includes: HD Video Processing Subsystem Dual Port Gigabit Ethernet MACs (10/100/1000 Mbps) [Ethernet Switch] with MII/RMII/GMII/RGMII and MDIO interface supporting IEEE 1588 Time-Stamping, AVB, and Industrial Ethernet ProtocolsTwo USB ports with integrated 2.0 PHY PCIe x1 GEN2 Compliant interfaceTwo 10-serializer McASP audio serial ports (with DIT mode)Four quad-serilaizer McASP audio serial ports (with DIT mode)One McBSP multichannel buffered serial portSix UARTs with IrDA and CIR supportFour SPI serial interfacesThree MMC/SD/SDIO serial interfacesFour I2C master and slave interfaces Parallel Camera Interface (CAM)Up to 128 General-Purpose I/Os (GPIOs)Eight 32-bit general-purpose timers System watchdog timer Dual DDR2, and DDR3 SDRAM interfacesFlexible 8- or 16-bit asynchronous memory interfaceTwo Controller Area Network (DCAN) modulesSpin LockMailbox

The TMS320DM8127 DaVinci Digital Media processors also include a high-definition video and imaging coprocessor 2 (HDVICP2) to off-load many video and imaging processing tasks from the DSP core, making more DSP MIPS available for common video and imaging algorithms. Additionally, the TMS320DM8127 DaVinci Digital Media processors have a complete set of development tools for both the ARM and DSP which include C compilers, a DSP assembly optimizer to simplify programming and scheduling, and a Microsoft® Windows™ debugger interface for visibility into source code execution.

The C674x DSP core is the high-performance floating-point DSP generation in the TMS320C6000 DSP platform and is code-compatible with previous generation C64x Fixed-Point and C67x Floating-Point DSP generation. The C674x Floating-Point DSP processor uses 32KB of L1 program memory with EDC and 32KB of L1 data memory. Up to 32KB of L1P can be configured as program cache. The remaining memory is noncacheable no-wait-state program memory. Up to 32KB of L1D can be configured as data cache. The remaining memory is noncacheable no-wait-state data memory. The DSP has 256KB of L2 RAM with ECC, which can be defined as SRAM, L2 cache, or a combination of both. All C674x L3 and off-chip

TMS320DM8127 DaVinci Digital Media processors are highly integrated, programmable platforms that leverage the technology to meet the processing needs of the following applications to name a few:IP Network Cameras Industrial Automation Network Cameras Stereo Cameras Video Surveillance HD Video Conferencing Car Black BoxHome Audio and Video Equipment

The device enables Original-Equipment Manufacturers (OEMs) and Original-Design Manufacturers (ODMs) to quickly bring to market devices featuring robust operating systems support, rich user interfaces, and high processing performance through the maximum flexibility of a fully integrated mixed processor solution. The device also combines programmable video and audio processing with a highly integrated peripheral set.

Programmability is provided by an ARM Cortex-A8 RISC CPU with Neon extension, TI C674x VLIW floating-point DSP core, and high-definition video and imaging coprocessors. The ARM lets developers keep control functions separate from A/V algorithms programmed on the DSP and coprocessors, thus reducing the complexity of the system software. The ARM Cortex-A8 32-Bit RISC Core with Neon floating-point extension includes: 32KB of Instruction cache; 32KB of Data cache; 256KB of L2 Cache; 48KB of Boot ROM; and 64KB of RAM.

The rich peripheral set provides the ability to control external peripheral devices and communicate with external processors. For details on each of the peripherals, see the related sections in this document and the associated peripheral reference guides. The peripheral set includes: HD Video Processing Subsystem Dual Port Gigabit Ethernet MACs (10/100/1000 Mbps) [Ethernet Switch] with MII/RMII/GMII/RGMII and MDIO interface supporting IEEE 1588 Time-Stamping, AVB, and Industrial Ethernet ProtocolsTwo USB ports with integrated 2.0 PHY PCIe x1 GEN2 Compliant interfaceTwo 10-serializer McASP audio serial ports (with DIT mode)Four quad-serilaizer McASP audio serial ports (with DIT mode)One McBSP multichannel buffered serial portSix UARTs with IrDA and CIR supportFour SPI serial interfacesThree MMC/SD/SDIO serial interfacesFour I2C master and slave interfaces Parallel Camera Interface (CAM)Up to 128 General-Purpose I/Os (GPIOs)Eight 32-bit general-purpose timers System watchdog timer Dual DDR2, and DDR3 SDRAM interfacesFlexible 8- or 16-bit asynchronous memory interfaceTwo Controller Area Network (DCAN) modulesSpin LockMailbox

The TMS320DM8127 DaVinci Digital Media processors also include a high-definition video and imaging coprocessor 2 (HDVICP2) to off-load many video and imaging processing tasks from the DSP core, making more DSP MIPS available for common video and imaging algorithms. Additionally, the TMS320DM8127 DaVinci Digital Media processors have a complete set of development tools for both the ARM and DSP which include C compilers, a DSP assembly optimizer to simplify programming and scheduling, and a Microsoft® Windows™ debugger interface for visibility into source code execution.

The C674x DSP core is the high-performance floating-point DSP generation in the TMS320C6000 DSP platform and is code-compatible with previous generation C64x Fixed-Point and C67x Floating-Point DSP generation. The C674x Floating-Point DSP processor uses 32KB of L1 program memory with EDC and 32KB of L1 data memory. Up to 32KB of L1P can be configured as program cache. The remaining memory is noncacheable no-wait-state program memory. Up to 32KB of L1D can be configured as data cache. The remaining memory is noncacheable no-wait-state data memory. The DSP has 256KB of L2 RAM with ECC, which can be defined as SRAM, L2 cache, or a combination of both. All C674x L3 and off-chip | 1 GHz, 750 MHz | 90 °C | -40 °C | 1.5 V, 1.8 V, 3.3 V | 1.15 V | 832 kB | ROM | Digital Media System-on-Chip (DMSoC) | 684-FCBGA | Surface Mount | 684-BFBGA, FCBGA | CAN, Ethernet, I2C, McASP, McBSP, MMC/SD, SPI, UART, USB | 48 kB | 23 | 23 | |||||||||||||||||||||||||||||||||||||||||

Texas Instruments TMS320F2810PBKQThe TMS320F2810, TMS320F2811, and TMS320F2812-Q1 devices, members of the TMS320C28x DSP generation, are highly integrated, high-performance solutions for demanding control applications.

Throughout this document, TMS320F2810, TMS320F2811, and TMS320F2812-Q1 are abbreviated as F2810, F2811, and F2812-Q1, respectively. F281x denotes all three devices.

The TMS320F2810, TMS320F2811, and TMS320F2812-Q1 devices, members of the TMS320C28x DSP generation, are highly integrated, high-performance solutions for demanding control applications.

Throughout this document, TMS320F2810, TMS320F2811, and TMS320F2812-Q1 are abbreviated as F2810, F2811, and F2812-Q1, respectively. F281x denotes all three devices. | 125 °C | -40 °C | 128-LQFP (14x14) | Surface Mount | 128-LQFP | CANbus, McBSP, SCI, SPI, UART/USART | 32-Bit Single-Core | FLASH | 18 K | Internal | 56 | 150 MHz | 1.81 V | 2 V | DMA, POR, PWM, WDT | C28x | 12 b, 16 | Automotive | AEC-Q100 | |||||||||||||||||||||||||||||||||||||

Texas Instruments TMS320F28063PNTC28x C2000™ C28x Piccolo™ Microcontroller IC 32-Bit Single-Core 90MHz 128KB (64K x 16) FLASH 80-LQFP (12x12) | 105 °C | -40 °C | Surface Mount | 80-LQFP | 32-Bit Single-Core | FLASH | 34 K | Internal | 40 | 90 MHz | 1.71 V | 1.995 V | Brown-out Detect/Reset, DMA, POR, PWM, WDT | C28x | 12 bits | 12 | CANbus | UART/USART | SCI | SPI | I2C | McBSP | ||||||||||||||||||||||||||||||||||

Texas Instruments TMS320DM6435ZDU7The TMS320C64x+™ DSPs (including the TMS320DM6435 device) are the highest-performance fixed-point DSP generation in the TMS320C6000™ DSP platform. The DM6435 device is based on the third-generation high-performance, advanced VelociTI™ very-long-instruction-word (VLIW) architecture developed by Texas Instruments (TI), making these DSPs an excellent choice for digital media applications. The C64x+™ devices are upward code-compatible from previous devices that are part of the C6000™ DSP platform. The C64x™ DSPs support added functionality and have an expanded instruction set from previous devices.

Any reference to the C64x DSP or C64x CPU also applies, unless otherwise noted, to the C64x+ DSP and C64x+ CPU, respectively.

With performance of up to 4800 million instructions per second (MIPS) at a clock rate of 600 MHz, the C64x+ core offers solutions to high-performance DSP programming challenges. The DSP core possesses the operational flexibility of high-speed controllers and the numerical capability of array processors. The C64x+ DSP core processor has 64 general-purpose registers of 32-bit word length and eight highly independent functional units–two multipliers for a 32-bit result and six arithmetic logic units (ALUs). The eight functional units include instructions to accelerate the performance in video and imaging applications. The DSP core can produce four 16-bit multiply-accumulates (MACs) per cycle for a total of 2400 million MACs per second (MMACS), or eight 8-bit MACs per cycle for a total of 4800 MMACS. For more details on the C64x+ DSP, see the TMS320C64x/C64x+ DSP CPU and Instruction Set Reference Guide (literature number SPRU732).

The DM6435 also has application-specific hardware logic, on-chip memory, and additional on-chip peripherals similar to the other C6000 DSP platform devices. The DM6435 core uses a two-level cache-based architecture. The Level 1 program memory/cache (L1P) consists of a 256K-bit memory space that can be configured as mapped memory or direct mapped cache, and the Level 1 data (L1D) consists of a 640K-bit memory space–384K-bit of which is mapped memory and 256K-bit of which can be configured as mapped memory or 2-way set-associative cache. The Level 2 memory/cache (L2) consists of a 1M-bit memory space that is shared between program and data space. L2 memory can be configured as mapped memory, cache, or combinations of the two.

The peripheral set includes: a configurable video port (VPFE); a 10/100 Mb/s Ethernet MAC (EMAC) with a management data input/output (MDIO) module; a 4-bit transmit, 4-bit receive VLYNQ interface; an inter-integrated circuit (I2C) Bus interface; a multichannel buffered serial port (McBSP); a multichannel audio serial port (McASP0) with 4 serializers; 2 64-bit general-purpose timers each configurable as 2 independent 32-bit timers; 1 64-bit watchdog timer; a user-configurable 16-bit host-port interface (HPI); up to 111-pins of general-purpose input/output (GPIO) with programmable interrupt/event generation modes, multiplexed with other peripherals; 2 UARTs with hardware handshaking support on 1 UART; 3 pulse width modulator (PWM) peripherals; 1 high-end controller area network (CAN) controller [HECC]; and 2 glueless external memory interfaces: an asynchronous external memory interface (EMIFA) for slower memories/peripherals, and a higher speed synchronous memory interface for DDR2.

The DM6435 device includes a Video Processing Subsystem (VPSS) with a configurable video/imaging front-end input peripheral used for video capture.

The Video Processing Front-End (VPFE) is comprised of a CCD Controller (CCDC), a Preview Engine (Previewer), Histogram Module, Auto-Exposure/White Balance/Focus Module (H3A), and Resizer. The CCDC is capable of interfacing to common video decoders, CMOS sensors, and Charge Coupled Devices (CCDs). The Previewer is a real-time image processing engine that takes raw imager data from a CMOS sensor or CCD and converts from an RGB Bayer Pattern to YUV422. The Histogram and H3A modules provide statistical information on the raw color data for use by the DM6435. The Resizer accepts image data for separate horizontal and vertical resizing from 1/4x to 4x in increments of 256/N, where N is between 64 and 1024.

The Ethernet Media Access Controller (EMAC) provides an efficient interface between the DM6435 and the network. The DM6435 EMAC support both 10Base-T and 100Base-TX, or 10 Mbits/second (Mbps) and 100 Mbps in either half- or full-duplex mode, with hardware flow control and quality of service (QOS) support.

The Management Data Input/Output (MDIO) module continuously polls all 32 MDIO addresses in order to enumerate all PHY devices in the system.

The I2C and VLYNQ ports allow DM6435 to easily control peripheral devices and/or communicate with host processors.

The high-end controller area network (CAN) controller [HECC] module provides a network protocol in a harsh environment to communicate serially with other controllers, typically in automotive applications.

The rich peripheral set provides the ability to control external peripheral devices and communicate with external processors. For details on each of the peripherals, see the related sections later in this document and the associated peripheral reference guides.

The DM6435 has a complete set of development tools. These include C compilers, a DSP assembly optimizer to simplify programming and scheduling, and a Windows™ debugger interface for visibility into source code execution.

The TMS320C64x+™ DSPs (including the TMS320DM6435 device) are the highest-performance fixed-point DSP generation in the TMS320C6000™ DSP platform. The DM6435 device is based on the third-generation high-performance, advanced VelociTI™ very-long-instruction-word (VLIW) architecture developed by Texas Instruments (TI), making these DSPs an excellent choice for digital media applications. The C64x+™ devices are upward code-compatible from previous devices that are part of the C6000™ DSP platform. The C64x™ DSPs support added functionality and have an expanded instruction set from previous devices.

Any reference to the C64x DSP or C64x CPU also applies, unless otherwise noted, to the C64x+ DSP and C64x+ CPU, respectively.

With performance of up to 4800 million instructions per second (MIPS) at a clock rate of 600 MHz, the C64x+ core offers solutions to high-performance DSP programming challenges. The DSP core possesses the operational flexibility of high-speed controllers and the numerical capability of array processors. The C64x+ DSP core processor has 64 general-purpose registers of 32-bit word length and eight highly independent functional units–two multipliers for a 32-bit result and six arithmetic logic units (ALUs). The eight functional units include instructions to accelerate the performance in video and imaging applications. The DSP core can produce four 16-bit multiply-accumulates (MACs) per cycle for a total of 2400 million MACs per second (MMACS), or eight 8-bit MACs per cycle for a total of 4800 MMACS. For more details on the C64x+ DSP, see the TMS320C64x/C64x+ DSP CPU and Instruction Set Reference Guide (literature number SPRU732).

The DM6435 also has application-specific hardware logic, on-chip memory, and additional on-chip peripherals similar to the other C6000 DSP platform devices. The DM6435 core uses a two-level cache-based architecture. The Level 1 program memory/cache (L1P) consists of a 256K-bit memory space that can be configured as mapped memory or direct mapped cache, and the Level 1 data (L1D) consists of a 640K-bit memory space–384K-bit of which is mapped memory and 256K-bit of which can be configured as mapped memory or 2-way set-associative cache. The Level 2 memory/cache (L2) consists of a 1M-bit memory space that is shared between program and data space. L2 memory can be configured as mapped memory, cache, or combinations of the two.

The peripheral set includes: a configurable video port (VPFE); a 10/100 Mb/s Ethernet MAC (EMAC) with a management data input/output (MDIO) module; a 4-bit transmit, 4-bit receive VLYNQ interface; an inter-integrated circuit (I2C) Bus interface; a multichannel buffered serial port (McBSP); a multichannel audio serial port (McASP0) with 4 serializers; 2 64-bit general-purpose timers each configurable as 2 independent 32-bit timers; 1 64-bit watchdog timer; a user-configurable 16-bit host-port interface (HPI); up to 111-pins of general-purpose input/output (GPIO) with programmable interrupt/event generation modes, multiplexed with other peripherals; 2 UARTs with hardware handshaking support on 1 UART; 3 pulse width modulator (PWM) peripherals; 1 high-end controller area network (CAN) controller [HECC]; and 2 glueless external memory interfaces: an asynchronous external memory interface (EMIFA) for slower memories/peripherals, and a higher speed synchronous memory interface for DDR2.

The DM6435 device includes a Video Processing Subsystem (VPSS) with a configurable video/imaging front-end input peripheral used for video capture.

The Video Processing Front-End (VPFE) is comprised of a CCD Controller (CCDC), a Preview Engine (Previewer), Histogram Module, Auto-Exposure/White Balance/Focus Module (H3A), and Resizer. The CCDC is capable of interfacing to common video decoders, CMOS sensors, and Charge Coupled Devices (CCDs). The Previewer is a real-time image processing engine that takes raw imager data from a CMOS sensor or CCD and converts from an RGB Bayer Pattern to YUV422. The Histogram and H3A modules provide statistical information on the raw color data for use by the DM6435. The Resizer accepts image data for separate horizontal and vertical resizing from 1/4x to 4x in increments of 256/N, where N is between 64 and 1024.

The Ethernet Media Access Controller (EMAC) provides an efficient interface between the DM6435 and the network. The DM6435 EMAC support both 10Base-T and 100Base-TX, or 10 Mbits/second (Mbps) and 100 Mbps in either half- or full-duplex mode, with hardware flow control and quality of service (QOS) support.

The Management Data Input/Output (MDIO) module continuously polls all 32 MDIO addresses in order to enumerate all PHY devices in the system.

The I2C and VLYNQ ports allow DM6435 to easily control peripheral devices and/or communicate with host processors.

The high-end controller area network (CAN) controller [HECC] module provides a network protocol in a harsh environment to communicate serially with other controllers, typically in automotive applications.

The rich peripheral set provides the ability to control external peripheral devices and communicate with external processors. For details on each of the peripherals, see the related sections later in this document and the associated peripheral reference guides.

The DM6435 has a complete set of development tools. These include C compilers, a DSP assembly optimizer to simplify programming and scheduling, and a Windows™ debugger interface for visibility into source code execution. | 700 MHz | 90 °C | 0 °C | 1.8 V, 3.3 V | 1.05 V, 1.2 V | 240 kB | Fixed Point | 376-BGA (23x23) | Surface Mount | 376-BBGA Exposed Pad | 10/100 Ethernet MAC, HPI, I2C, McASP, McBSP, UART | 64 kB | ||||||||||||||||||||||||||||||||||||||||||||

Texas Instruments TMS320DM648CUT1 | 1.1 GHz | 90 °C | 0 °C | 1.8 V, 3.3 V | 1.2 V | 576 kB | Fixed Point | 529-FCBGA (19x19) | Surface Mount | 529-BFBGA | Host Interface, I2C, McASP, PCI, SPI, UART | 64 kB | ||||||||||||||||||||||||||||||||||||||||||||

Texas Instruments TMS320F28032RSHSC2000™ 32-bit microcontrollersare optimized for processing, sensing, and actuation to improve closed-loop performance inreal-time control applicationssuch asindustrial motor drives;solar inverters and digital power;electrical vehicles and transportation;motor control; andsensing and signal processing. The C2000 line includes thePremium performance MCUsand theEntry performance MCUs.

The F2803x family of microcontrollers provides the power of the C28x core and Control Law Accelerator (CLA) coupled with highly integrated control peripherals in low pin-count devices. This family is code-compatible with previous C28x-based code, and also provides a high level of analog integration.