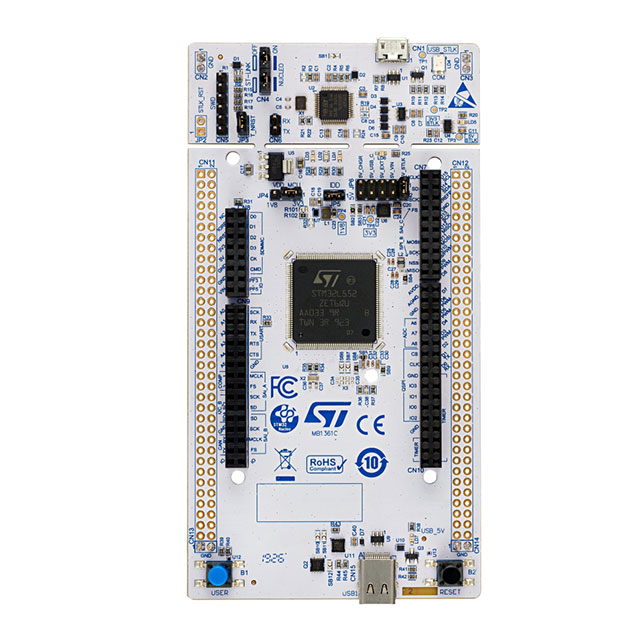

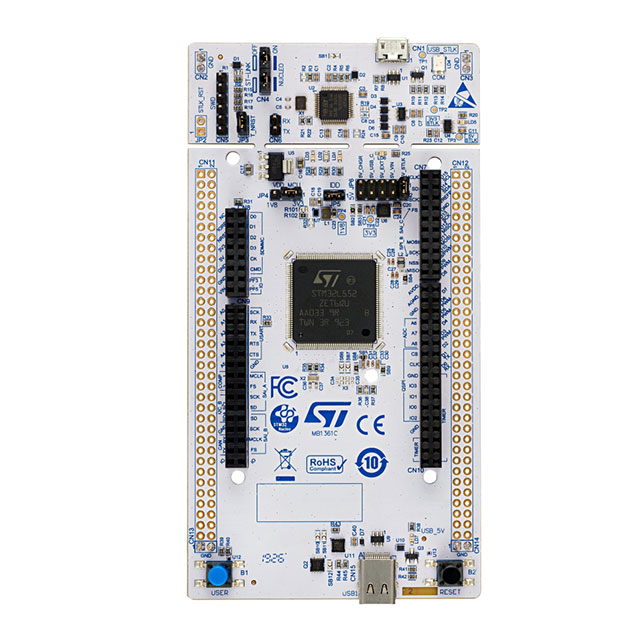

NUCLEO-L552ZE-Q

ActiveSTM32 NUCLEO-144 DEVELOPMENT BOARD WITH STM32L552ZE MCU, SMPS, SUPPORTS ARDUINO, ST ZIO AND MORPHO CONNECTIVITY

Deep-Dive with AI

Search across all available documentation for this part.

NUCLEO-L552ZE-Q

ActiveSTM32 NUCLEO-144 DEVELOPMENT BOARD WITH STM32L552ZE MCU, SMPS, SUPPORTS ARDUINO, ST ZIO AND MORPHO CONNECTIVITY

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

| Specification | NUCLEO-L552ZE-Q |

|---|---|

| Board Type | Evaluation Platform |

| Contents | Board(s) |

| Core Processor | ARM® Cortex®-M33 |

| Interconnect System | ST Zio, Arduino R3 Shield, ST Morpho |

| Mounting Type | Fixed |

| Platform | Nucleo-144 |

| Suggested Programming Environment | STM32Cube, Keil MDK, IAR EW |

| Type | MCU 32-Bit |

| Utilized IC / Part | STM32L552 |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

| Digikey | Bulk | 1 | $ 21.28 | |

Description

General part information

NUCLEO-L552ZE-Q Series

The STM32L552xx devices are an ultra-low-power microcontrollers family (STM32L5 Series) based on the high-performance Arm®Cortex®-M33 32-bit RISC core. They operate at a frequency of up to 110 MHz.

The Cortex®-M33 core features a single-precision floating-point unit (FPU), which supports all the Arm®single-precision data-processing instructions and all the data types. The Cortex®-M33 core also implements a full set of DSP (digital signal processing) instructions and a memory protection unit (MPU) which enhances the application’s security.

These devices embed high-speed memories (512 Kbytes of Flash memory and 256 Kbytes of SRAM), a flexible external memory controller (FSMC) for static memories (for devices with packages of 100 pins and more), an Octo-SPI Flash memories interface (available on all packages) and an extensive range of enhanced I/Os and peripherals connected to two APB buses, two AHB buses and a 32-bit multi-AHB bus matrix.

Documents

Technical documentation and resources