Technical Specifications

Parameters and characteristics for this part

| Specification | STM6905TGEDS6F |

|---|---|

| Mounting Type | Surface Mount |

| Number of Voltages Monitored | 5 |

| Operating Temperature [Max] | 85 °C |

| Operating Temperature [Min] | -40 °C |

| Output | Open Drain or Open Collector |

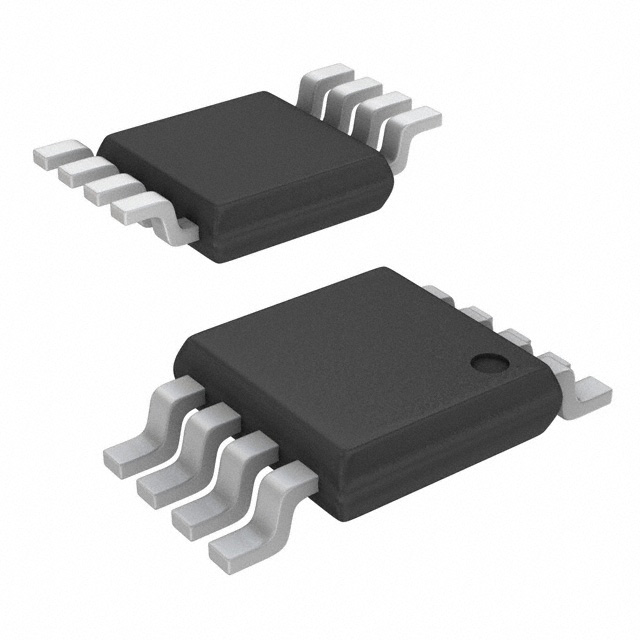

| Package / Case | 8-MSOP, 8-TSSOP |

| Package / Case | 3 mm |

| Package / Case [custom] | 0.118 in |

| Reset | Active Low |

| Reset Timeout [Min] | 140 ms |

| Supplier Device Package | 8-MSOP |

| Type | Multi-Voltage Supervisor |

| Voltage - Threshold | Adj |

| Voltage - Threshold | 1.11 V, 3.078 V |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

| Digikey | Cut Tape (CT) | 1 | $ 2.10 | |

| 10 | $ 1.89 | |||

| 25 | $ 1.78 | |||

| 100 | $ 1.51 | |||

| 250 | $ 1.42 | |||

| 500 | $ 1.24 | |||

| 1000 | $ 1.03 | |||

| Digi-Reel® | 1 | $ 2.10 | ||

| 10 | $ 1.89 | |||

| 25 | $ 1.78 | |||

| 100 | $ 1.51 | |||

| 250 | $ 1.42 | |||

| 500 | $ 1.24 | |||

| 1000 | $ 1.03 | |||

| Tape & Reel (TR) | 4000 | $ 0.95 | ||

| 8000 | $ 0.91 | |||

Description

General part information

STM6905 Series

The STM6905 supervisor is a low voltage/low supply current processor supervisor, designed to monitor up to five system power supply voltages. This device is targeted at applications such as set-top boxes (STBs), portable, battery-powered systems, networking and communication systems.

The device supports a push-button type manual reset input (MR). Two of the five supply monitors (VCCand V2IN) have fixed (customer-selectable, factory-trimmed) thresholds (VRST1and VRST2). The other three voltage monitor inputs (V3IN, V4IN and V5IN) are monitored using externally adjustable threshold (600 mV internal reference) to meet specific level requirements.

If any of the five monitored voltages drops below its factory-trimmed or adjustable thresholds, or if theMRis asserted to logic low, the reset outputRSTis asserted (driven low). Once asserted,RSTis maintained low for a minimum delay period (tREC) after ALL monitored supplies rise above their respective thresholds andMRreturns to high. The reset output logic state is valid for VCCgreater than 0.8 V.

Documents

Technical documentation and resources