SY87701LHG

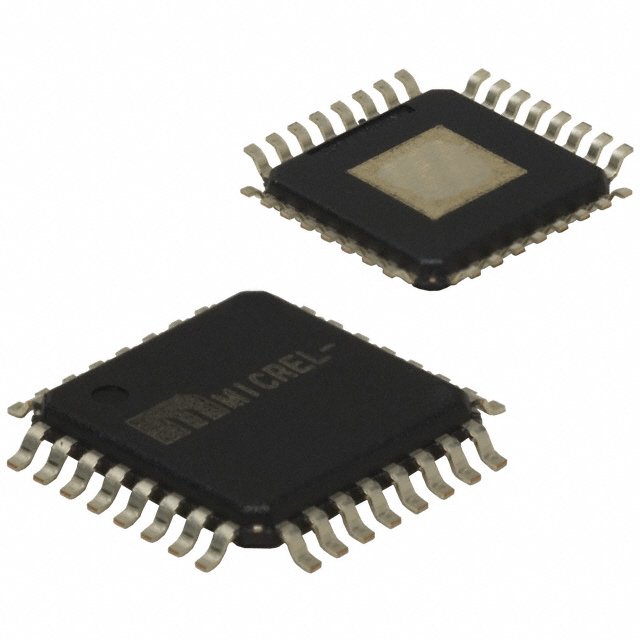

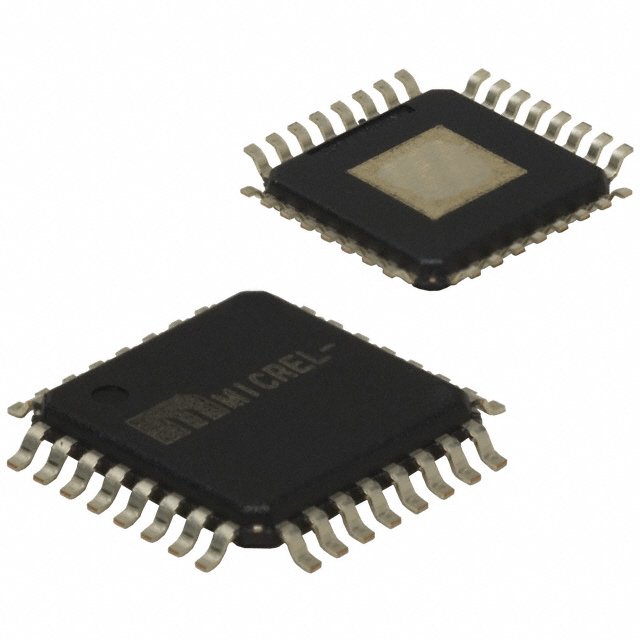

ActiveCLOCK & DATA RECOVERY IC, 1.25 GBPS, 3.15 V TO 3.45 V, 32 PINS, TQFP-EP

Deep-Dive with AI

Search across all available documentation for this part.

SY87701LHG

ActiveCLOCK & DATA RECOVERY IC, 1.25 GBPS, 3.15 V TO 3.45 V, 32 PINS, TQFP-EP

Deep-Dive with AI

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

Description

General part information

SY87701 Series

The SY87701L is a complete Clock Recovery and Data Retiming integrated circuit for data rates from 32Mbps up to 1.25Gbps NRZ. The device is ideally suited for SONET/SDH/ATM and Fibre Channel applications and other high-speed data transmission systems. Clock recovery and data retiming is performed by synchronizing the on-chip VCO directly to the incoming data stream. The VCO center frequency is controlled by the reference clock frequency and the selected divide ratio. On-chip clock generation is performed through the use of a frequency multiplier PLL with a byte rate source as reference. The SY87701L also includes a link fault detection circuit.Industrial temperature range (-40°C to +85°C) 3.3V power supply Clock and data recovery from 32Mbps up to 1.25Gbps NRZ data stream, clock generation from 32Mbps to 1.25Gbps Complies with Bellcore, ITU/CCITT and ANSI specifications for applications such as OC-1, OC-3, OC-12, ATM, FDDI, Fibre Channel and Gigabit Ethernet as well as proprietary applications Two on-chip PLLs: one for clock generation and another for clock recovery Selectable reference frequencies Differential PECL high-speed serial I/O Line receiver input: no external buffering needed Link fault indication 100k ECL compatible I/O Available in 32-pin EPAD-TQFP and 28-pin SOIC packages (28-pin SOIC is available, but NOT recommended for new designs.)

Documents

Technical documentation and resources